张宗兵理解的ANSYS芯片-单板-整机SIPI、EMC电磁仿真解决方案

责任编辑:

沙克

时间:2023-04-30

来源:转载于:仿真秀APP公众号

责任编辑:

沙克

时间:2023-04-30

来源:转载于:仿真秀APP公众号

导读:集成电路(Integrated Circuit)是一种微型电子器件或部件。是典型的知识密集型、技术密集型、资本密集和人才密集型的高科技产业。它是一种微型电子器件或部件,采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。它在电路中用字母“IC”表示。

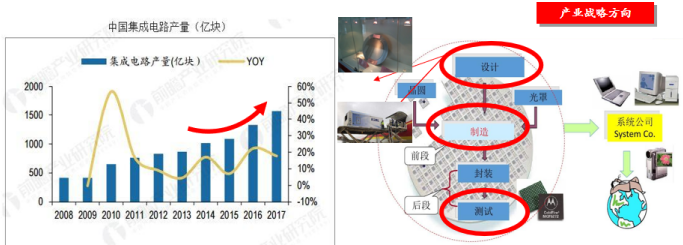

根据相关权威机构行业调研,提供了如下数据:

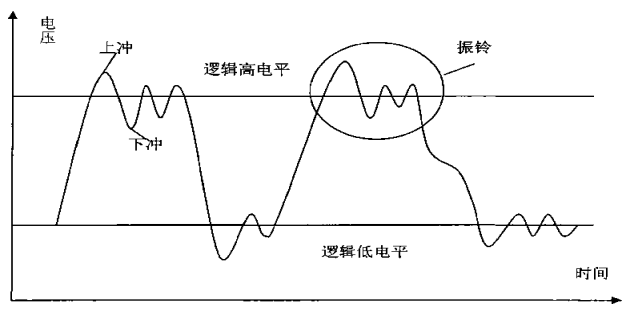

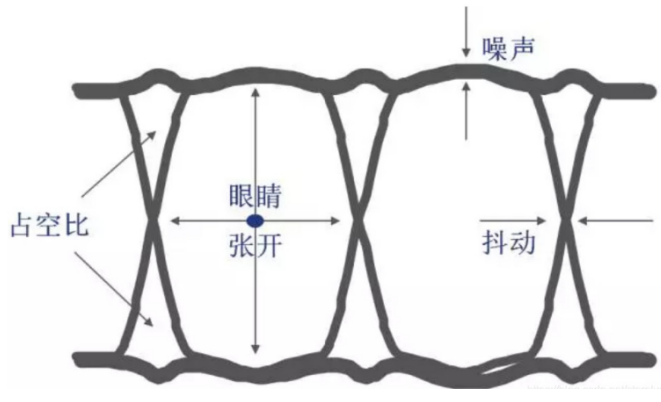

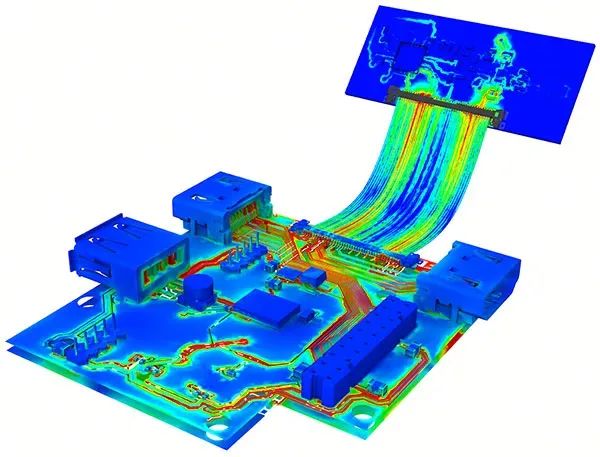

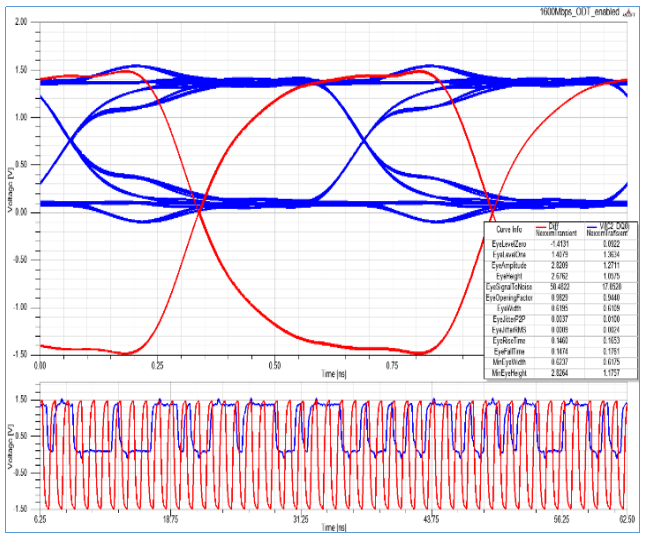

从数据中可以看出,电子技术及信息化产业日趋发达,集成电路产量逐年稳健增长!《国家集成电路产业发展推进纲要》明确提出在 IC设计、制造、封装、测试等领域重点发展,构建竞争力产业链!研发生产制造全流程端到端工艺复杂,大规模投入先进制造技术提升的同时,前端充分的可靠性设计也是重中之重! 现阶段,电子系统正向高速化和高密度化飞跃发展。在电子系统的设计过程中, 系统的体积越来越小,IC引脚(integrated circuit,集成电路)却越来越多,因此PCB (Printed Circuit Board,印制电路板)上的元件与布线越来越密集;与此同时,信号的 时钟频率越来越大,并且信号上升沿越来越陡峭。这些因素都导致了电磁环境的日益 复杂,设备之间以及设备内部因互感和互容引发的种种电磁兼容问题已不容忽视。 这一问题在现今的强辐射源与高功率微波系统中也显得日益突出。如在某高功率微波系 统中,需要在限定的体积和尺寸下,采用FPGA芯片实现对多路电机的并行控制,就需要设计高速高密度的PCB。本文就研究该情况下PCB的板级电磁兼容问题,主要包括信号完整性(Signal Integrity, SI)和电源完整性(PowerIntegrity,PD问题。 信号完整性概括地说,是指信号在信号线上传输质量的好坏。在数字电路中,体 现在信号能在电路中能以正确的电压、带宽和时序做出响应。若在PCB中,信号可以以正确的电压大小、带宽和时序都到达接收端,就能说明该PCB具有较好的信号完整性。如果不能,则说明PCB中岀现了严重的信号完整性问题。 在高速高密度的数字电路中,信号完整性问题大致表现在一下几个方面:振铃、 过冲、欠冲和时延等。为了正确读取数据并对数据进行处理,数据在集成电路中需要 在时钟边沿的前后处于稳定状态。这个时间段内,如果信号不稳定或者发生状态的改 变,集成电路就可能误判甚至发生丢失部分数据的情况,影响信号的正常传输。如图 1所示,若岀现振铃、上冲或下冲等信号完整性问题,就会影响数据的正常传输,从 而影响PCB的正常工作,也可以从眼图直观判断信号传输的好坏,如图2

图1 PCB中信号完整性问题的表现

信号完整性问题既会导致信号明显的失真和时序混乱,也会造成数据的错误,从 而造成系统出错甚至瘫痪。通常,在数字芯片中,高于VIH的电平被称为逻辑“1”, 而低于VIL的电平被称为逻辑“0”,在逻辑高电平与逻辑低电平之间的电平是不确定状态。对于有振铃的数字信号,当振荡电平进入逻辑高电平与逻辑低电平之间的不确定区时,会引起逻辑错误。 为了保证电子系统的正常工作,数字信号要求了正确的时序。为了保证正确的逻辑时序,一般的数字芯片都要求信号需要在时钟触发边缘到达前达到稳定。如果信号传输延时的部分太长,那么,在时钟的上升沿或下降沿处就或许不能接收到正确的逻辑,将会引起错误的时序。引起信号完整性问题的因素有很多, 元器件的参数、PCB上元器件的布局、层叠结构、高速信号线在PCB±的如何布线等 都是影响信号完整性的关键因素。 电源完整性指的是信号传播时电源的纹波质量。现阶段电源完整性问题主要研究 的方面是同步开关噪声(Simultaneous Switch Noise, SSN)。在数字电路中,工作过 程中的门电路会发生从高电平到低电平或者从低电平到高电平的转换,从而造成瞬间 的变化电流A7o A/在流经返回路径时会由于返回路径的电感产生压降,从而引起噪声。如果在同一时刻有多个引脚发生状态转换,产生的压降足以引起严重的电源完整性问题。 电源完整性问题不仅仅关乎到PCB的馈电电压,也影响了整个电子系统的设计。 电源分配网络和各种互连结构构成了 PCB的主要噪声耦合途径。电源噪声会在电源平 面/地平面腔体内产生谐振,并通过传输线、过孔等结构传播,以电源平面/地平面上 返回路径造成电压压降的形式破坏电源分配网络或信号线的良好传输。主要的噪声产 生源之一为高速数字元器件,高速数字元器件通过电源分配网络与其它元件发生耦合, 这种耦合将会引起严重的PLL (Phase Locked Loop,锁相环)抖动,继而导致时序容 限和噪声裕量的减小。有些电压噪声发生在谐振频点处,这还会在间接引起严重的电 磁干扰问题。由于超摩尔定律的不断作用,在系统封装尺寸减小的情况下,系统功率又逐步增大,复杂度越来越高,噪声耦合也越来越强,因此在电子系统的设计中,设计要求更高。

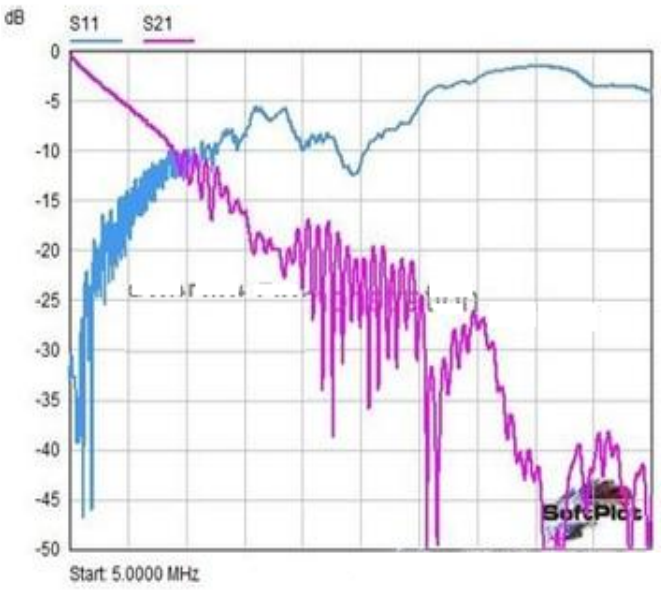

在设计前期,仿真技术可以校核前期信号传输载体的合规性,通过前期仿真模拟可以有效减少后期样品的电源信号完整性问题,一个集成电路,只要解决了信号电源完整性问题,EMC问题,从信号传输角度讲,就解决了集成电路的高性能问题。 在前期集成电路预研阶段,需要对已经设计的芯片封装PCB做仿真模拟,信号完整性领域主要分析对象为高速/高频信号、多负载信号网络、复杂的信号通道结构。主要分析内容为反射、串扰、过冲/振铃、通道阻抗、时序/抖动、损耗,对信号完整性影响要素繁多,包括:多负载拓扑、走线换层、参考层不连续、线间距过小、高密度连接器、差分线失配、走线过长、PCB板厚、材质选用、存在木桩、过孔大小、BGA出线、芯片封装等等,在前期仿真模拟阶段有大量的工作需要仿真模拟并校核。

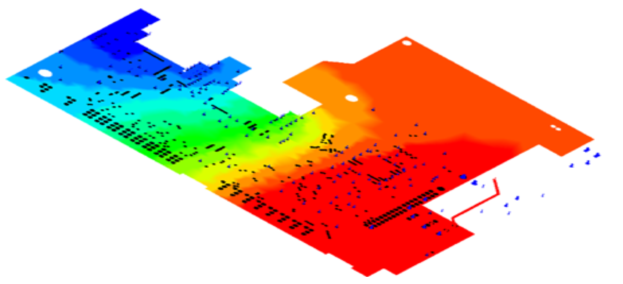

时域眼图

频域S参数及插损

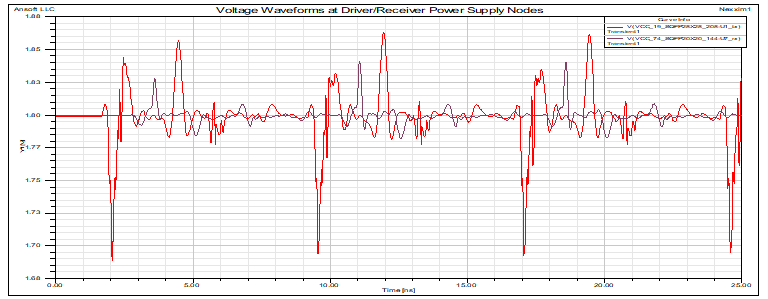

电源完整性领域主要分析对象有高速/高频数字芯片的供电网络、大电流低电压电源网络、数/模电路隔离,主要分析内容为:谐振分析、电源平面阻抗曲线、直流压降/电流密度、频域噪声隔离度、电源地噪声/SSN,影响电源完整性的要素主要有退耦电容容值、电容摆放位置、电容布线方式、芯片摆放位置、叠层设计情况、电源地层分配、电源地线宽度、换层过孔数量、数模隔离方式等等,往往对于一个复杂的PCB封装系统,需要做多要素研究,研究不同要素对电源完整性影响大小。

电压密度电压跌落

电源纹波图

来源:转载于:仿真秀APP公众号